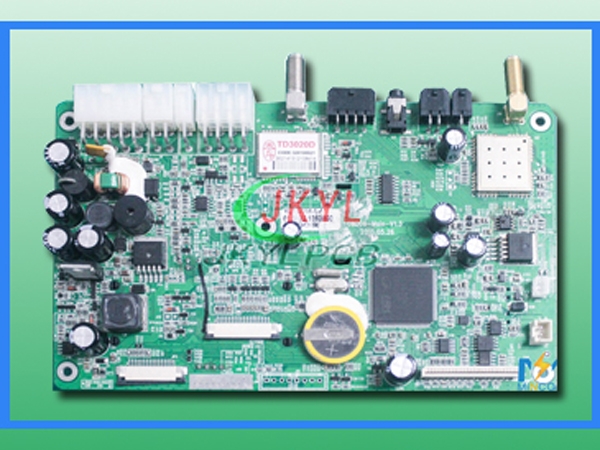

当提到PCBA上的电子电路时,经常使用的术语是杂散电容。PCB上的导体、无元器件的预制电路板、PCBA、有安装元器件的板之间以及元器件封装(尤其是IC)中的SMD组件套件之间可能存在杂散电容。杂散电容是电子电路和电路板固有的那些物理属性之一。那么如何减少PCB杂散电容的影响呢?

1、移除内层接地层

由于接地层会由于邻近而增加与相邻导体的电容,因此删除内层接地层以增加距离会有所帮助,这将使电容效应最小化。这必须与最小化接地平面与信号平面相邻时获得的EMI的好处进行权衡。

2、使用法拉第盾

法拉第屏蔽是放置在两条迹线之间以最小化它们之间的电容效应的接地迹线或平面,并且像其他屏蔽结构一样,它可以有效地减小杂散电容。

3、增加相邻迹线之间的空间

另一种有效的缓解技术是增加相邻迹线之间的间距。随着电容随着距离的增加而减小,这是可以应用的非常好的方法。

4、尽量减少使用过孔

通孔是使紧凑,复杂的PCB成为可能的关键要素。但是,过度使用可能会增加寄生电容问题。例如杂散电容。通过消除在没有连接的层上的过孔周围的环形环并最大程度地减少来自组件的过孔数量,可以减少这种PTH耦合。如BGA。

以上便是今天分享的减少PCB杂散电容的方法